Simpelweg brute rekenkracht en kolossaal veel data toevoegen: die aanpak werkte lange tijd prima voor de ontwikkeling van Large Language Models. Je voegt meer GPU's, data en trainingstijd toe et voilà: model x.0 is geboren.

Maar er komt roest op de formule. Nu we verder evolueren van generatieve AI richting redenerende modellen, wordt de werklast van modellen steeds heterogener. Agentic AI, gericht op besluitvorming en zeer relevant voor medische toepassingen, en physical AI, gericht op interactie met de fysieke wereld, bijvoorbeeld voor robotica en autonome auto's, vereisen een hele ketting van verschillende modellen die elk een specifiek doel dienen en met elkaar interageren: een AI-systeem dat grote taalmodellen, perceptiemodellen en actiemodellen kan combineren. Sommige modellen vereisen CPU’s, andere GPU’s en weer andere modellen missen momenteel de juiste processors. Deze observatie zette NVIDIA's Jensen Huang ertoe aan om te stellen dat we uiteindelijk een oplossing met drie computers nodig zouden hebben om de volgende generatie AI te kunnen draaien.

Het is duidelijk dat een klassieke “one size fits all”-aanpak met alleen meer rekenkracht niet zal volstaan. AI is nu al een middelgroot land (vergelijkbaar met Japan) als het gaat om energieverbruik. De kern van dit energievraagstuk is dat systemen vaak draaien op een suboptimale computerarchitectuur, bestaande uit suboptimale hardwarecomponenten voor de specifieke werklast die de algoritmes vragen. Door nieuwe, uitdagende workloads aan de mix toe te voegen, zal het AI-gerelateerde energieverbruik naar alle verwachting exponentieel stijgen.

Wat het allemaal extra uitdagend maakt, is het feit dat AI-workloads van de ene dag op de andere kunnen veranderen, aangestuurd door een nieuw algoritme. Denk maar aan het verhaal van de Chinese start-up Deepseek, die een enorme schokgolf door de hele industrie stuurde door plots verbluffende resultaten te bereiken met een fractie van de rekenkracht van de concurrenten. En, wat ook in het oog sprong: in minder dan twee weken werd dat resultaat alweer gereproduceerd door andere laboratoria. Algoritmebouwers schakelen inderdaad snel. Hardwareproblemen zijn een stuk tijdrovender: het duurt al snel meerdere jaren om kleine verbeteringen te realiseren. Bovendien wordt hardware-optimalisatie steeds complexer en duurder.

Het is bijzonder moeilijk te voorspellen wat de volgende hardwarevereiste zal zijn in de snel evoluerende wereld van AI. Op de lange termijn is flexibiliteit de sleutel.

Met andere woorden: de techindustrie zit met een synchronisatieprobleem. Het ontwikkelen van een specifieke rekenchip voor elk model - zoals we nu doen voor generatieve AI - kan het tempo van innovatie in AI-modellen onmogelijk bijhouden. En de wetten van de economie spelen ook niet in het voordeel: er is een enorm inherent risico omdat de AI-softwaregemeenschap een andere wending kan hebben genomen tegen de tijd dat de AI-hardware klaar is. Hoe kunnen AI-bedrijven de ontwikkelingstijd van AI-hardware versnellen? Eén manier is om het zelf te doen: OpenAI begint samen met TSMC met de ontwikkeling van hun eigen AI-chips op maat. Het blijft echter een kostbare en riskante onderneming, vooral geschikt voor bedrijven die veel gewicht en geld in de schaal kunnen leggen.

Het is bijzonder moeilijk te voorspellen wat de volgende hardwarevereiste zal zijn in de snel evoluerende wereld van AI. Op de lange termijn is flexibiliteit de sleutel. Hardware moet bijna net zo 'codeerbaar' worden als software. Dezelfde set hardwarecomponenten moet herconfigureerbaar zijn. Dit betekent dat je niet drie computers nodig hebt om een reeks algoritmen uit te voeren, maar slechts één wendbaar exemplaar. Eigenlijk zou software de configuratie van chips moeten definiëren. Dat is een heel andere benadering dan de huidige hardware-innovatie, die een vrij stroef proces is.

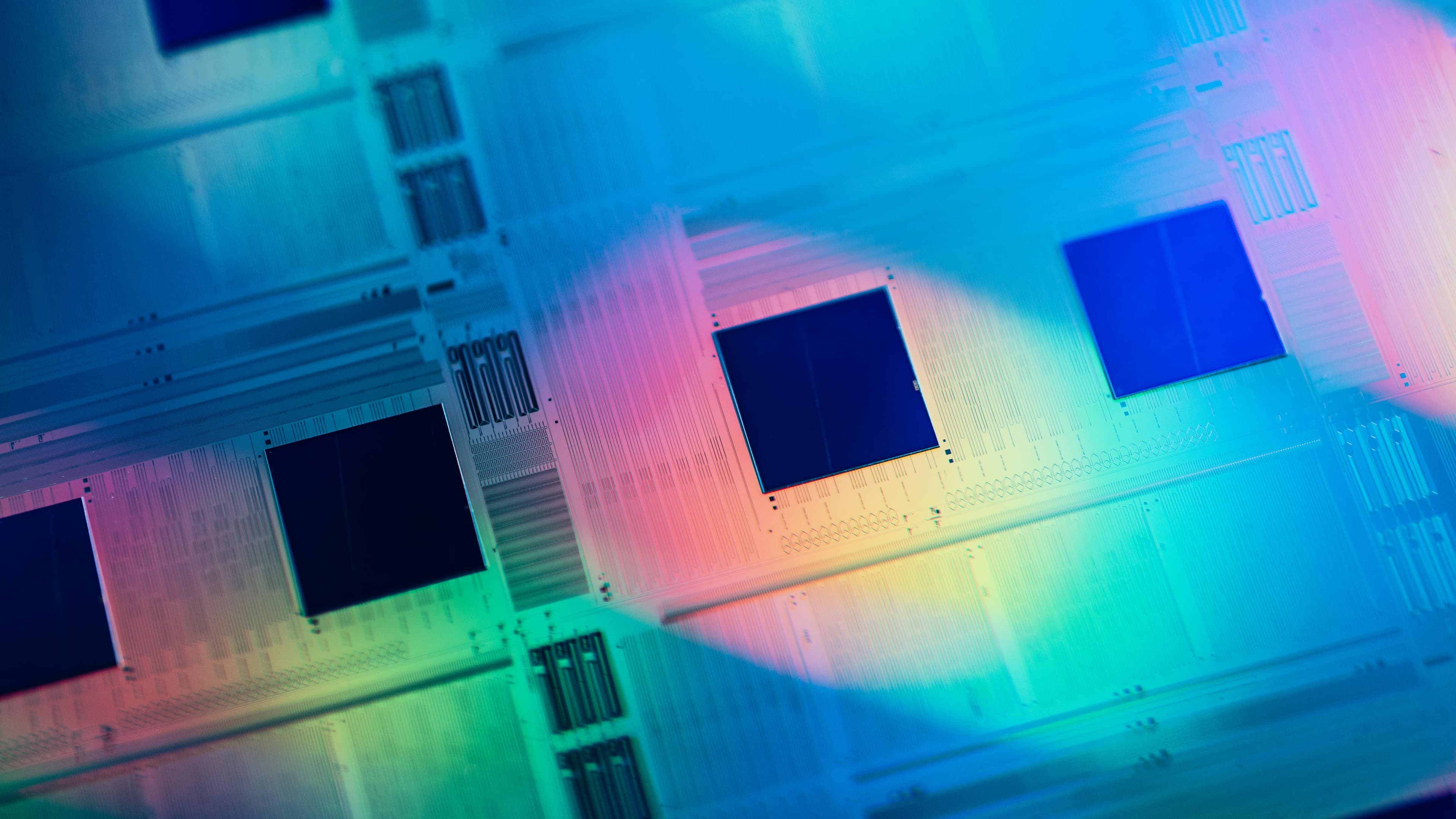

Stel je voor: in plaats van één monolithische 'state of the art' en superdure processor, zou je verschillende bouwstenen krijgen, geïntegreerd in 3D, zo gestapeld dat geheugen- en rekenchips dicht bij elkaar kunnen worden geplaatst, waardoor het energieverlies van dataverkeer wordt beperkt. Door de verschillende bouwstenen slim te combineren kunnen ze snel worden aangepast aan de nieuwste algoritme-eisen,.

Tegelijk worden nieuwe geheugentechnologieën mogelijk die beter geschikt zijn voor AI. imec's spin-off Vertical Compute integreert bijvoorbeeld verticale datalanes rechtstreeks bovenop de rekeneenheden, waardoor de afstand die data moet afleggen aanzienlijk wordt verminderd - van centimeters tot nanometers. Deze aanpak minimaliseert dataverplaatsingen, wat resulteert in energiebesparingen tot 80%. Het is slechts een van de vele manieren waarop hardware-innovatie next-gen AI mogelijk zal maken.

Met deze herconfigureerbare aanpak zullen veel meer bedrijven hun eigen hardware kunnen ontwerpen voor specifieke AI-opdrachten. Daarnaast wordt het makkelijker om hardware van verschillende leveranciers te combineren.

Het zal de creativiteit in de markt alleen maar stimuleren, mogelijkheden bieden om te differentiëren en hardware-innovatie weer betaalbaar maken. Door het eens te worden over een universeel geaccepteerde standaard, zoals RISC-V, komen software- en hardwarebedrijven op één lijn en garanderen ze zowel compatibiliteit als topprestaties – wat uiteindelijk het enige is dat een eindgebruiker zal merken.

De imec-pilootlijn binnen het Europese NanoIC-project zal een Europees industrieel ecosysteem bevorderen van start-ups, AI-bedrijven, chipontwerpers, fabrikanten enzovoort - rond de meest geavanceerde technologie.

De imec-pilootlijn binnen het Europese NanoIC-project, is het Europese antwoord op de AI-gedreven complexiteit en versterkt Europa's leiderschap in onderzoek, door de kloof van laboratoria naar productie te overbruggen. Tegelijkertijd zal de pilootlijn een Europees industrieel ecosysteem bevorderen van start-ups, AI-bedrijven, chipontwerpers, fabrikanten enzovoort - rond de meest geavanceerde technologie.

De toekomst van AI hangt af van hardware-innovaties. En gezien de enorme impact van AI in alle maatschappelijke geledingen, variërend van het ontwerpen van medicijnen in silico tot sensorfusie voor robotica en autonoom rijden, is het waarschijnlijk niet overdreven om te stellen dat ook onze toekomst ervan afhangt.

Dit artikel verscheen eerder in Trends.

Luc Van den hove is sinds 1 juli 2009 de CEO van imec. Daarvoor was hij executive vice president en chief operating officer. Hij trad in 1984 in dienst bij imec en begon zijn onderzoeksloopbaan op het gebied van silicide- en interconnecttechnologieën. In 1988 werd hij manager van de micro-patterning-groep van imec (lithografie, droog etsen); in 1996 werd hij afdelingsdirecteur van unit process step R&D; en in 1998 werd hij vicepresident van de divisie siliciumproces- en devicetechnologie. In januari 2007 werd hij benoemd tot EVP & COO van imec. Luc Van den hove behaalde zijn doctoraat in de elektrotechniek aan de KU Leuven.

In 2023 ontving hij de Robert N. Noyce-medaille voor zijn leiderschap bij het creëren van een wereldwijd onderzoeksecosysteem in nano-elektronica-technologie met toepassingen variërend van high-performance computing tot gezondheid.

In 2025 ontving hij de eretitel van de Vlaamse Gemeenschap als erkenning voor zijn indrukwekkende rol in het versterken van Vlaanderen als toonaangevende innovatieve regio.

Hij is auteur en coauteur van meer dan 200 publicaties en conferentiebijdragen.

Vanaf april 2026 zal hij een nieuwe functie bekleden als voorzitter van de raad van bestuur van imec

Gepubliceerd op:

22 mei 2025