Historische overgang op komst

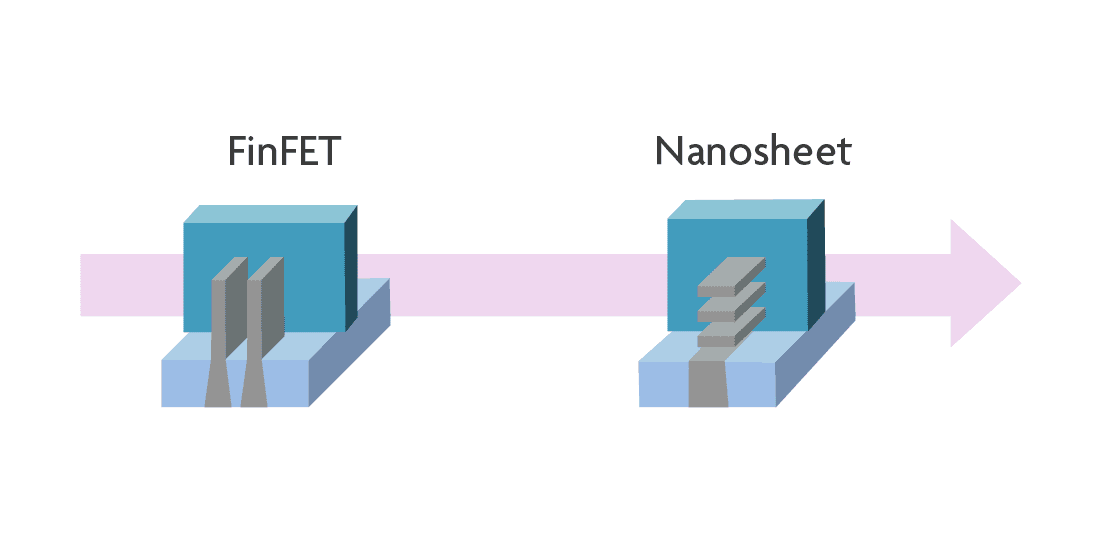

Het aantal transistoren op een chip verdubbelt zowat om de twee jaar, waardoor er steeds meer rekenkracht op een kleinere oppervlakte beschikbaar wordt. Chips alsmaar krachtiger maken (door de transistoren te verkleinen) is nodig om een antwoord te bieden op het toenemend dataverkeer, en om innovaties mogelijk te maken in domeinen als gezondheidzorg, mobiliteit, enz. Op een bepaald punt botsen we echter op fysieke limieten en moeten er nieuwe transistoren ontwikkeld worden die deze schaalverkleining kunnen voortzetten. Vandaag vinden we in de meest geavanceerde chips voor rekentoepassingen (de technologiegeneraties van 5 en 7 nanometer) de FinFET terug. De FinFET dankt zijn naam aan een geleidingskanaal dat de vorm heeft van een ‘vin’.

De chipindustrie staat echter nooit te popelen om een nieuw type transistor in gebruik te nemen voor de massaproductie van chips. Dat maakt het productieproces immers veel complexer en brengt extra investeringen met zich mee. Maar recent kondigden enkele grote chipfabrikanten zoals Samsung, Intel, TSMC en IBM aan dat zo’n overgang er binnenkort aankomt. Vanaf 2022 of 2023 zullen deze bedrijven gradueel de vertrouwde FinFET-transistor ‘inruilen’ voor de nanosheet-transistor. Deze ‘nanosheets’ zullen het kloppend hart vormen van de rekenchips van de 3nm of 2nm technologiegeneratie.

Vanaf 2022 of 2023 zullen enkele grote chipfrabrikanten gradueel de vertrouwde FinFET-transistor ‘inruilen’ voor de nanosheet-transistor.

In dit artikel verneem je de drijfveren achter deze historische overgang. We stellen ook verschillende generaties van de nanosheet-familie voor, namelijk de ‘gewone’ nanosheet, de forksheet en de CFET (of complementaire veldeffect-transistor). Voor elk van deze nanosheet-familieleden leggen we uit hoe ze stapsgewijs bijdragen tot de verdere evolutie van chips, en zetten we enkele kritische processtappen in de kijker.

Waarom de FinFET ‘inruilen’ voor de nanosheet?

Een manier om alsmaar meer transistoren op eenzelfde chipoppervlak te krijgen, is het verkleinen van de afmetingen van de standaardcellen. Een standaardcel is een kleine functionele eenheid van een chip die een beperkte logische functie kan uitvoeren, bijv. een logische AND of OR. Zo’n cel bestaat uit een paar transistoren en enkele metaal-interconnectielagen om die transistoren te verbinden.

Schematische voorstelling van een logische standaardcellayout met FinFETs (CPP = contacted poly pitch, de afstand tussen de poortcontactjes van twee transistoren; FP = de afstand tussen twee ‘vinnen’; MP = afstand tussen twee metaallijntjes; celhoogte: aantal metaallijntjes per cel (of tracks, T) maal de afstand tussen de metaallijnen).

De standaardcel verkleinen kan door de ‘hoogte’ van de cel te reduceren. Bij een FinFET gebeurde dat door het aantal vinnen per transistor systematisch te verminderen. In het originele ontwerp van de FinFET werden 3 vinnen gebruikt om voldoende stroomsterkte te hebben. Maar om de standaardcel verder te verkleinen, werd dat aantal teruggebracht naar 2. Om voldoende stroomsterkte te behouden, werden de 2 vinnen wat hoger gemaakt. Deze trend zou zich kunnen doorzetten tot er 1 vin overblijft.

In FinFET-gebaseerde architecturen wordt het aantal vinnen per transistor systematisch verminderd om standaardcellen te kunnen verkleinen. Om de kleiner wordende stroomsterkte te compenseren, worden de vinnen hoger gemaakt

De stroomsterkte van FinFET-gebaseerde transistor-architecturen verder vergroten is echter een hele uitdaging. En daar komt de nanosheet-architectuur te hulp. In deze transistor heeft het geleidingskanaal de vorm van een heel klein ‘velletje’ of nanosheet. Je kan nu verschillende nanosheets verticaal op elkaar stapelen, en elk van de nanosheets wat breder maken. Op die manier haal je meer stroom uit de transistor dan bij een FinFET, zonder zijn voetafdruk te moeten vergroten.

Uit een nanosheet-transistor haal je meer stroom dan uit een FinFET-transistor, zonder zijn voetafdruk te moeten vergroten.

Een ander belangrijk voordeel van de nanosheet is de zogenaamde ‘gate-all-around’-structuur: de poort (of gate) van de transistor omgeeft de geleidingskanaaltjes nu aan alle kanten, terwijl dat bij de FinFET maar aan drie kanten het geval was. Zo kan de poort veel meer controle over het geleidingskanaal uitoefenen, wat minder lekstromen geeft als de transistor uit staat. De nanosheet biedt dus ook een oplossing voor de ongewenste ‘korte-kanaaleffecten’ die optreden bij hele kleine transistoren.

Van FinFET naar nanosheet...

Kritische bouwstenen

Net zoals bij de overgang van de klassieke MOSFET-transistor naar de FinFET, moesten er voor de overgang van FinFET naar de ‘gate-all-around’ nanosheet-transistor een aantal nieuwe processtappen worden ontwikkeld. Maar gelukkig bleef dat aantal beperkt, aangezien de nanosheet vanuit fabricagestandpunt op een natuurlijke manier voortvloeit uit de FinFET. Heel wat van de procesmodules die destijds ontwikkeld en geoptimaliseerd zijn voor de FinFET konden dus hergebruikt worden. En dat heeft zeker de nakende overstap voor de industrie vergemakkelijkt. Toch zijn er een aantal kritische processtappen waarin beide architecturen verschillen, en die specifieke innovaties vereisten. Hierop heeft imec een belangrijke stempel gedrukt.

Als eerste stap in het fabricageproces worden verschillende lagen van Si en SiGe alternerend op elkaar neergezet. SiGe zal in een latere fase worden weggeëtst, waarna verschillende Si geleidingskanaaltjes (verticaal gestapeld) overblijven. Deze stapel aan multilagen wordt door middel van etstechnieken omgevormd tot een hoge en smalle structuur, waardoor het moeilijk wordt om de vorm van de nanosheet te behouden. Imec heeft hiervoor in 2017 tijdens een toonaangevende conferentie (IEDM) een oplossing voorgesteld die ook tot een betere werking van de transistor leidde: een grotere stroomsterkte en snellere schakeling. Imec was ook de eerste die de integratie van een goed werkende nanosheet-transistor in een echt circuit (m.n. een ringoscillator) rapporteerde. [1,2,3]

Imec kon als eerste de integratie van een goed werkende nanosheet-transistor in een reëel circuit (m.n. een ringoscillator) rapporteren.

Andere kritische processtappen zijn: de vorming van de ‘inner spacer’ (een module die de poort van de bron en afvoer moet isoleren); de ‘channel release’-stap (de stap waarin de nanosheets van elkaar gescheiden worden door de SiGe-laagjes selectief weg te etsen), en de integratie van de poortstructuur (waarbij het poortmetaal tussen en rond de nanosheets moet worden aangebracht). Imec heeft belangrijke bijdragen geleverd aan de ontwikkeling van elk van deze processtappen [2, 4].

Voorbeelden van optimalisaties voor verticaal gestapelde gate-all-around nanosheet-transistoren: (links) naar een betere controle van de vorm van de nanosheet; (rechts) naar een kleinere afstand tussen nanosheets.

En dan komt de forksheet

De beste manier om de transistoren beter te laten werken, is de effectieve breedte van de kanalen verder verhogen, zonder daarbij de standaardcel te vergroten. Maar in conventionele nanosheet-architecturen is dat heel moeilijk. Spelbreker is de grote ruimte die nodig is tussen de p- en n-type transistoren (in een standaard CMOS-rekenchip hebben we beide types nodig).

En daar komt de forksheet-transistor te hulp. Deze architectuur, uitgevonden door imec, laat toe om de n- en p-type transistoren dichter bij elkaar te brengen door een isolerende muur tussen de twee types transistoren te plaatsen. De vrijgekomen ruimte kan zo gebruikt worden om de effectieve kanaalbreedte verder te vergroten, waardoor de stroomsterkte toeneemt. Of, de kleinere ruimte tussen n en p kan ingezet worden om de hoogte van de standaardcel weer wat te verkleinen. De ontwerper heeft dus de vrijheid om met die parameters te spelen. Simulaties voorspellen ook dat de forksheet sneller zou kunnen schakelen dan een gewone nanosheet-transistor [5, 6].

De forksheet-architectuur, uitgevonden door imec, laat toe om de n- en p-type transistoren dichter bij elkaar te brengen door een isolerende muur tussen de twee types transistoren te plaatsen.

Vanuit fabricagestandpunt vloeit de forksheet-architectuur heel natuurlijk voort uit de conventionele nanosheet-architectuur. Al zijn er ook hier een aantal nieuwe processtappen, zoals de vorming van de isolerende muur. Tijdens een toonaangevende conferentie (VLSI 2021) kon imec voor de eerste keer de succesvolle integratie van forksheet-transistoren aantonen, evenals een elektrische karakterisatie. De afstand tussen de n- en p-type transistoren kon hierbij teruggebracht worden tot slechts 17nm [7].

Toch bleef er nog één bezorgdheid. Zoals eerder uitgelegd is de ‘gate-all-around’-structuur een belangrijke troef van de nanosheet-architectuur omdat die een goede elektrostatische controle van het geleidingskanaal mogelijk maakt. Maar bij de forksheet heeft de poortstructuur de vorm van een vork – vandaar ook de naam – en omgeeft die het kanaal maar aan drie kanten. Imec kon echter aantonen dat de controle over het kanaal voor een forksheet (met 20nm poortlengte) vergelijkbaar is met die van verticaal gestapelde nanosheet-transistoren [8].

Doorsnede (TEM) van forksheet- (links) en nanosheet- (rechts) transistoren die op één wafer werden geïntegreerd. Voor de forksheet werd de afstand tussen de p- en n-type transistoren verkleind tot 17nm.

Op langere termijn kan de CFET de nanosheet-familie vervolledigen

Met de complementaire veldeffect-transistor of CFET zullen we de effectieve kanaalbreedte nog verder kunnen vergroten. In deze architectuur worden de n- en p-type transistoren boven op elkaar gestapeld. Op die manier verplaatst de afstand tussen de n- en p-type transistoren zich nu naar de verticale richting, en moeten we hem niet meer in rekening brengen bij het bepalen van de cel-hoogte. Zo wordt ruimte vrijgemaakt om de kanaalbreedte verder te vergroten. De winst in oppervlakte kan ook hier weer gebruikt worden om de standaardcel verder te verkleinen [9, 10]. In de CFET kunnen kanalen gemaakt worden in de vorm van een vin (n-vin op p-vin) of in de vorm van een nanosheet (n-sheet op p-sheet). In deze laatste configuratie vervolledigt de CFET de nanosheet-familie als ultieme CMOS-transistorarchitectuur.

Evolutie van FinFET naar nanosheet, forksheet en CFET.

De CFET-architectuur is echter vrij complex om te maken. Om een verticale integratie van de twee types transistoren mogelijk te maken, kunnen we twee mogelijke integratieschema’s volgen – monolitisch en sequentieel – elk met zijn voor- en nadelen. Imec richt zich op de ontwikkeling van de specifieke modules en integratiestappen, en brengt de voor- en nadelen van elk van de procesflows in kaart. Op die manier levert het team een belangrijke bijdrage aan de realisatie van de CFET [11, 12, 13, 14, 15].

TEM-beelden van een ‘monolitische’ CFET. Links: bovenste CFET-transistor; rechts: onderste CFET-transistor.

Besluit

In dit artikel hebben we uitgelegd hoe de nanosheet-architectuur een verdere schaalverkleining van rekenchips mogelijk maakt. Elke nieuwe generatie – mogelijk gemaakt door de nanosheet, forksheet en CFET – zorgt voor beter werkende transistoren en/of een verdere verkleining van de hoogte van de standaardcel. Vanuit fabricagestandpunt vloeit de nanosheet op natuurlijke wijze voort uit de FinFET. Toch brengt elke nanosheet-architectuur specifieke integratie-uitdagingen met zich mee. Imec blijft zich inzetten om hiervoor oplossingen te ontwikkelen, voor- en nadelen af te wegen, en de resultaten terug te koppelen aan zijn partners uit de chipindustrie.

Dit artikel werd gepubliceerd in EngineeringNet.

Meer weten?

Referenties:

[1] ‘Gate-all-around MOSFETs based on vertically stacked horizontal Si nanowires in a replacement metal gate process on bulk Si substrates’, H. Mertens et al, VLSI 2016

[2] ‘Vertically stacked gate-all-around Si nanowire transistors: Key Process Optimizations and Ring Oscillator Demonstration’, H. Mertens et al, IEDM 2017

[3] ‘Vertically Stacked Gate-All-Around Si Nanowire CMOS Transistors with Reduced Vertical Nanowires Separation, New Work Function Metal Gate Solutions, and DC/AC Performance Optimization’, R. Ritzenthaler et al, IEDM 2018

[4] ‘Power-performance trade-offs for Lateral NanoSheets on ultra-scaled standard cells’, M. Garcia Bardon, VLSI 2018

[5] ‘Stacked nanosheet fork architecture for SRAM design and device co-optimization toward 3nm’, P. Weckx et al, IEDM 2017

[6] ‘Novel forksheet device architecture as ultimate logic scaling device towards 2nm’, P. Weckx et al, IEDM 2019

[7] ‘Forksheet FETs for Advanced CMOS Scaling: Forksheet-Nanosheet Co-Integration and Dual Work Function Metal Gates at 17nm N-P Space’, H. Mertens et al, VLSI 2021

[8] “Comparison of Electrical Performance of Co-Integrated Forksheets and Nanosheets Transistors for the 2nm Technological Node and Beyond”, R. Ritzenthaler et al, IEDM 2021

[9] ‘The Complementary FET (CFET) for CMOS scaling beyond N3’, J. Ryckaert et al, VLSI 2018

[10] ‘Device-, Circuit- & Block-level evaluation of CFET in a 4 track library’ P. Schuddinck et al, VLSI 2019

[11] ‘First Monolithic Integration of 3D Complementary FET (CFET) on 300mm Wafers’, S. Subramanian et al, VLSI 2020

[12] ‘BTI Reliability Improvement Strategies in Low Thermal Budget Gate Stacks for 3D Sequential Integration’, J. Franco et al, IEDM 2018

[13] ‘Atomic Hydrogen Exposure to Enable High-Quality Low-Temperature SiO2 with Excellent pMOS NBTI Reliability Compatible with 3D Sequential Tier Stacking’, J. Franco et al, IEDM 2020

[14] ‘Contact Resistivity of Highly Doped Si:P, Si:As and Si:P:As Epi layers for Source/Drain Epitaxy’, E. Rosseel et al, ESC PRiME 2020

[15] ‘Very Low Temperature Epitaxy of Group-IV Semiconductors for use in FinFET, Stacked Nanowires and Monolithic 3D Integration’, C. Porret et al, ESC Journal of Solid State Science and Technology 2019

Meer informatie kan je vinden in onderstaand persbericht, en in enkele Engelstalige artikels op de imec website:

- ‘Imec demonstreert nieuw soort transistor die chips onder de 2 nanometer mogelijk maakt’, persbericht;

- ‘A view on the logic technology roadmap: advancing the front-end, back-end and middle-of-line towards the 1nm technology generation’, imec reading room;

- ‘Logic technology scaling options for 2nm and beyond’, imec reading room;

- ‘A novel approach for improving gate-stack reliability’, imec reading room.

Hij begon zijn loopbaan in halfgeleider R&D in Fujitsu Laboratories Ltd. in 1992. Van 1992-1999 richtte hij zich op de ontwikkeling van transistoren in Fujitsu Laboratories Ltd. en aan de Universiteit van California, Santa Barbara. Van 2000 tot 2006 leidde hij als integratie-ingenieur de ontwikkeling van 90-45nm CMOS-technologie in Fujitsu Ltd. Sinds 2006 is hij werkzaam bij imec, waar hij zich richt op onderzoek en ontwikkeling van geavanceerde CMOS-transistoren, samen met imecs wereldwijd ecosysteem van industriële partners, universiteiten en onderzoeksinstituten. Zijn huidige focus is de schaalverkleining van CMOS-transistoren voor de 1nm en kleinere technologienodes.

Gepubliceerd op:

31 mei 2022